Visible to Intel only — GUID: igo1517866620824

Ixiasoft

1. Introduction to Standard Edition Best Practices Guide

2. Reviewing Your Kernel's report.html File

3. OpenCL Kernel Design Best Practices

4. Profiling Your Kernel to Identify Performance Bottlenecks

5. Strategies for Improving Single Work-Item Kernel Performance

6. Strategies for Improving NDRange Kernel Data Processing Efficiency

7. Strategies for Improving Memory Access Efficiency

8. Strategies for Optimizing FPGA Area Usage

A. Additional Information

2.1. High Level Design Report Layout

2.2. Reviewing the Report Summary

2.3. Reviewing Loop Information

2.4. Reviewing Area Information

2.5. Verifying Information on Memory Replication and Stalls

2.6. Optimizing an OpenCL Design Example Based on Information in the HTML Report

2.7. HTML Report: Area Report Messages

2.8. HTML Report: Kernel Design Concepts

3.1. Transferring Data Via Channels or OpenCL Pipes

3.2. Unrolling Loops

3.3. Optimizing Floating-Point Operations

3.4. Allocating Aligned Memory

3.5. Aligning a Struct with or without Padding

3.6. Maintaining Similar Structures for Vector Type Elements

3.7. Avoiding Pointer Aliasing

3.8. Avoid Expensive Functions

3.9. Avoiding Work-Item ID-Dependent Backward Branching

4.3.4.1. High Stall Percentage

4.3.4.2. Low Occupancy Percentage

4.3.4.3. Low Bandwidth Efficiency

4.3.4.4. High Stall and High Occupancy Percentages

4.3.4.5. No Stalls, Low Occupancy Percentage, and Low Bandwidth Efficiency

4.3.4.6. No Stalls, High Occupancy Percentage, and Low Bandwidth Efficiency

4.3.4.7. Stalling Channels

4.3.4.8. High Stall and Low Occupancy Percentages

7.1. General Guidelines on Optimizing Memory Accesses

7.2. Optimize Global Memory Accesses

7.3. Performing Kernel Computations Using Constant, Local or Private Memory

7.4. Improving Kernel Performance by Banking the Local Memory

7.5. Optimizing Accesses to Local Memory by Controlling the Memory Replication Factor

7.6. Minimizing the Memory Dependencies for Loop Pipelining

Visible to Intel only — GUID: igo1517866620824

Ixiasoft

4.3.4.5. No Stalls, Low Occupancy Percentage, and Low Bandwidth Efficiency

Loop-carried dependencies might create a bottleneck in your design that causes an LSU or channel to have a low occupancy percentage and a low bandwidth.

Remember: An ideal kernel pipeline condition has a stall percentage of 0%, an occupancy percentage of 100%, and a bandwidth that equals the board's available bandwidth.

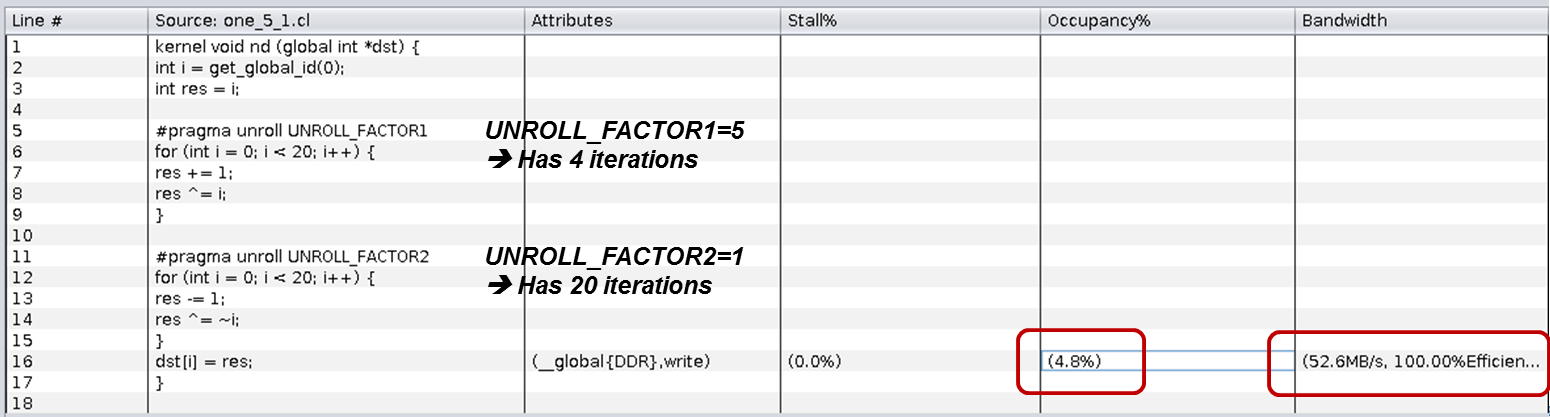

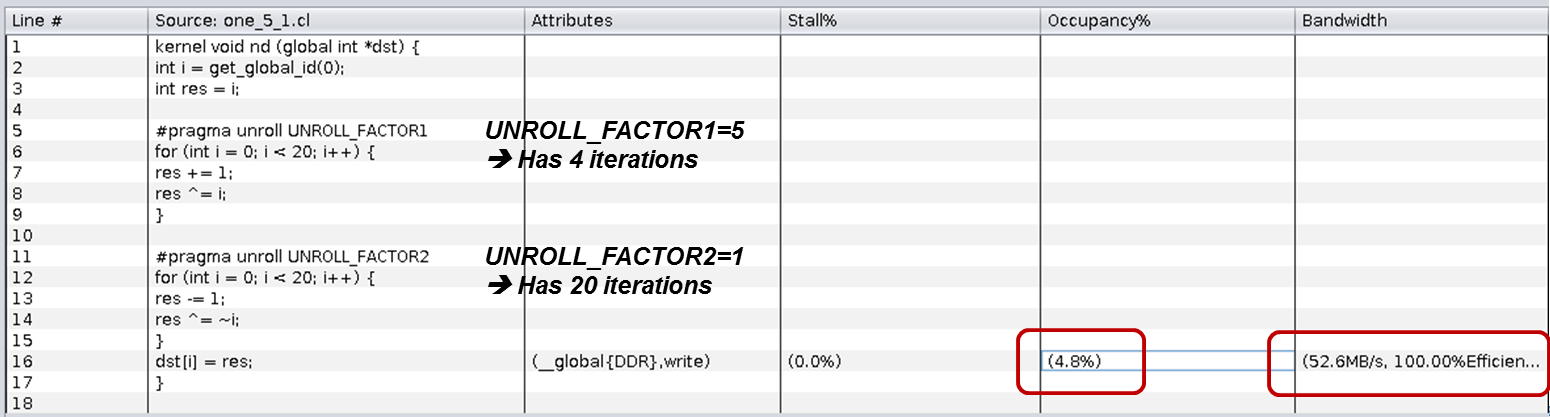

Figure 71. Example OpenCL Kernel and Profiler Analysis

In this example, dst[] is executed once every 20 iterations of the FACTOR2 loop and once every four iterations of the FACTOR1 loop. Therefore, FACTOR2 loop is the source of the bottleneck.

Solutions for resolving loop bottlenecks:

- Unroll the FACTOR1 and FACTOR2 loops evenly. Simply unrolling FACTOR1 loop further will not resolve the bottleneck

- Vectorize your kernel to allow multiple work-items to execute during each loop iteration

Related Information